|

可编程器件概述

可编程器件PLD(Programable Logic Device)是80年代发展起来的新型器件,PLD是一种由用户根据自己的需要来设计逻辑功能并对此器件进行编程后实现的。

数字电路的集成电路通常是标准的小规模、中规模、大规模的器件,而这些器件的逻辑功能是出厂时已经由厂商设计好了,用户只能根据其提供的功能及管脚进行设计其需要的电路,由于这些通用器件考虑到其通用性,其在使用时有许多功能是多余的,并且由于管脚的排布是固定的,在设计PCB时给电路的连线带来了极大不便,而PLD其内部具有大量组成数字电路的最小单元――门电路,而这些门电路并没有固定怎样连接,并且输入/输出脚的连接可自己设置,而这些门电路的连接是通过编程的方法加以设计,故这种电路给我们带来了极大的方便。

1.提高了功能的集成度

PLD器件较中小规模集成芯片具有更高的功能集成度,一般来说一片PLD器件可替代4~20片的中小规模集成芯片,而更大规模的PLD(如CPLD、FPGA)一般采用最新的集成电路生产工艺及技术,可达到极大的规模,这些器件的出现降低了电子产品的成本和缩小了电子产品的体积。

2.加快了电子系统的设计速度

一方面由于PLD器件集成度的提高,减小了电子产品设计中的布线时间及器件的安装时间;另一方面由于PLD器件的设计是利用计算机进行辅助设计的,其可以通过计算机的辅助设计软件对设计的电路进行仿真和模拟,减小了传统设计过程中的调试电路的时间,另外由于PLD器件是可擦除和可编程的,故即使设计有问题修改也是很方便的。

3.高的性能

由于PLD器件在生产过程中采用了最新的生产工艺及技术,故通过PLD器件的性能优于一般通用的器件,其速度一般比通用器件速度高一到两个数量级,另外由于器件数量的减少,降低的电路的总功耗。

4.高可靠性

系统的可靠性是数字系统的一项重要指标。根据可靠性理论可知器件的数量增加,系统的可靠性将下降;反之将提高。采用了PLD器件可减少器件的数量,器件的减少还导致PCB的布线减少,同时也减少了器件之间的交叉干扰和可能产生的噪声源,使系统运行更可靠。

5.成本低

由于PLD器件的上述优点将导致电子产品在设计、安装、调试、维修、器件品种库存等方面的成本下降,从而使电子产品的总成本降低,提高了产品的竞争力。

可编程逻辑器件的构成原理

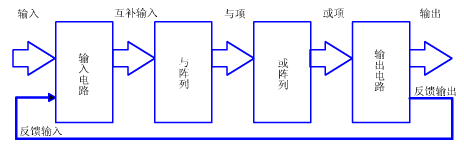

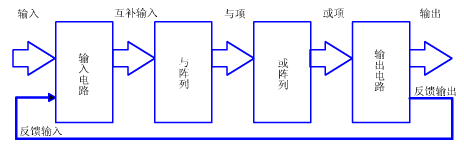

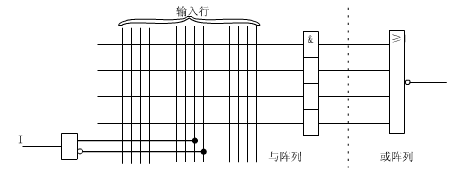

我们前面已经讲过了有关组成逻辑电路的分析及设计的内容,从前面的知识我们可知任一组成逻辑电路都可以写成与或表达式的形成(也可以是或与表达式的形式),我们欲实现组合逻辑的功能可将其分为与逻辑部分及或逻辑部分,于是实现任一组合逻辑电路按下图的步骤就可以实现了。

上图可分为输入电路、与阵列、或阵列、输出电路几部分。输入电路用于对输入信号进行缓冲,并产生原变量和反变量两个互补的信号供与阵列使用。与阵列和或阵列用于实现各种与或结构的逻辑函数,若进一步与逻辑电路的输出反馈电路配合可实现各种复杂的逻辑功能。输出电路则有多种形式,可以是三态门的输出;也可以是双向的输出;或是一个多功能的输出宏单元,使PLD的功能更加灵活、完善。

下表列出了常用的PLD内部的结构:

| 分类 |

与阵列 |

或阵列 |

输出电路 |

| PROM |

固定 |

可编程 |

固 定 |

| PLA |

可编程 |

可编程 |

固 定 |

| PAL |

可编程 |

固 定 |

固 定 |

| GAL |

可编程 |

固 定 |

可组态 |

PROM是由固定的与阵列和可编程的或阵列组成。当与阵列有n个输入时,就会有2n个输出(全译码输出),即要有2n个2输入的与门存在。由于PROM是直接利用未经化简与或表达式的每个最小项来实现,因而在门的利用率上常常是不经济的。PROM阵列的全译码功能更适合于作为存储器使用,现在很少作为PLD来使用。

PLA的与阵列和或阵列均可编程,因而可实现经过化简的与或逻辑,与、或阵列可得到充分使用,但迄今为止还没有高质量的编程工具,另外由于PLA的输出结构的缺陷,现在已很少使用了。

PAL是与项可编程、或项固定的,每个输出是输入变量若干个与或的形式。用户通过编程可实现各种组合逻辑电路。PAL一般采用熔断丝双极性工艺,只能一次编程。但由于其速度较快、开发系统完善,现仍有较少使用。

GAL的基本逻辑部分与PAL相同,也是与项可编程、或项固定。但其输出电路采用逻辑宏单元形式,用户可以对输出自行组态。GAL采用EEPROM的浮栅技术,实现了电可擦除功能,大大方便了用户的使用,现使用较广。

可编程器件的表示

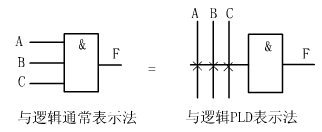

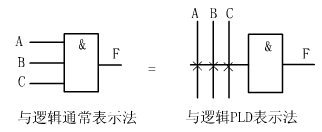

由于PLD器件的阵列规模较大,在描述PLD内部电路时采用通常的逻辑电路的表示方法将带来诸多不便,所以在讨论PLD器件时采用简化的表示方法。

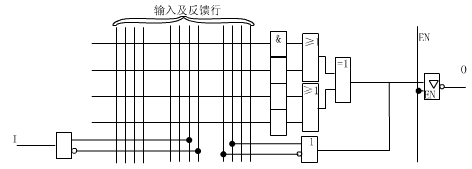

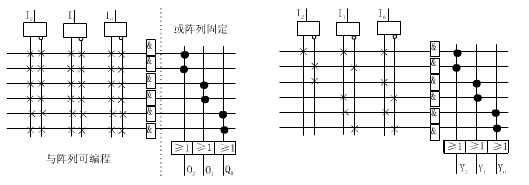

上图是PLD器件内部的简化表示方法,其每个结点分为三种情况:固定连接、不连接、编程连接。“固定连接”表示该结点的两条交叉的点是固定地连接着,可理解为通常电路中的连接焊点,不可以通过编程将其断开,通常用一个小圆点来表示;“编程连接”表示该结点的两条交叉线是通过编程的方法将其连接上的,当然其既然可以通过编程将其连接,同样可以通过编程将其断开,通常用一个叉来表示连接;“不连接”表示该结点的两条交叉的线互不相连或是通过编程将其断开,在两条线交叉点既没有交叉点又没有小圆点。PLD器件由于与项的项数较多,如果用常用表示方法,将给绘制PLD的内部图带来不便,故常用简化的表示方法,下图左右两图是等效的。

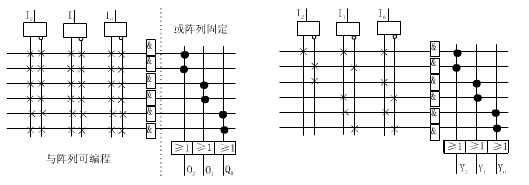

下面给出了两个图,左图给出的是PAL未编程时的内部结构图;右图为一个已经编程的内部结构图。

可编程器件的输出结构

可编程器件的不同,其输出结构也有所区别,这里以PAL器件为例讲述在组合逻辑电路中使用到的输出电路结构,其结构有如下几种:

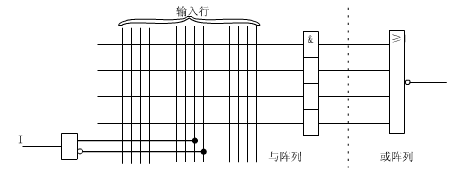

固定输出结构

固定输出结构是可编程器件中最简单的输出结构,其输出就是或阵列的输出,其可以实现简单的组合逻辑电路的功能,如下图所示:

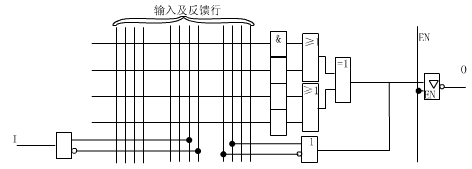

异步I/O输出结构

上面简单的固定输出结构只能实现简单的组合逻辑功能,如果希望实现其输出端既可以当输入使用,又可以作为输入端正使用,这时上面电路就无法实现了,这时须用异步I/O结构的输出结构。其图如下图所示。

从图上可以看出当其中的三态门的使能端为0时,其三态门处理高阻状态,其内部的输出与I/O线隔离,这时I/O可作为输入来使用;而当三态门的使用能端为1时,其I/O为输出,这时内部的逻辑功能不仅输出端I/O端,还反馈到其内部编程矩阵,这可以实现各种须带反馈的电路,从而减少电路的外部连接,如在RS触发器电路及各种带级联的电路。

带异或门的输出

带异或门的输出端加上了一个异或门,这个异或门的加入使得电路的构成发生了变化,如果一个逻辑函数需要的与项个数非常多(如一个四输入的函数,其与项的个数最多为16个),如果用反函数来实现时,发现其与项的个数较少(是16减去原函数的与项个数),异或门具有一个特点:当输入端的一个输入为0时,其输出等于另一个输入;而当输入端中的一个固定为1时,其输出为另一个输入的非。这异或门的引入使得用原函数实现函数困难时可以通过反函数加以实现。

|

Alexa

Alexa mcusy_cn#126.com (请把#改成@)

mcusy_cn#126.com (请把#改成@)  交流:522422171

交流:522422171 51/AVR单片机技术驿站! <

51/AVR单片机技术驿站! <

最新评论

最新评论 评论人:[匿名]

时间: [2012/9/28 4:59:16] IP:[111.223.37.19*]

评论人:[匿名]

时间: [2012/9/28 4:59:16] IP:[111.223.37.19*]