| 1��PLD��������Ʋ���

����1.��·����������

����PLD����������������һ���Ϊԭ��ͼ������Ӳ����������������ԭ��ͼ������һ��ֱ�ۼ��ķ����������Խ����е�С��ģ���ɵ�·ʵ�ֵĹ���ֱ����PLD������ʵ�֣�������ȥ�����еĵ�·������������������·ͼ��������������������Ӳ���������������ǿɱ��������Ƶ���һ�����������������������ܾ�ȷ�ͼ����ر�ʾ��·�������ܣ�������PLD����ƹ����й㷺ʹ�ã������и���䰵����ƣ����õ�Ӳ������������ABEL,VHDL���Եȣ�����ABEL��һ�ּ�Ӳ���������ԣ���֧�ֲ������̡���ֵ����״̬�����������������ڼ��������������������·���Ƚ����������ܵ�������VHDL������һ����Ϊ�������ԣ����̽ṹ�����ڼ�����е�C���ԣ����������������ʱ���dz���࣬���к�ǿ���������ͷ�����������δ��Ӳ��������Ե�������

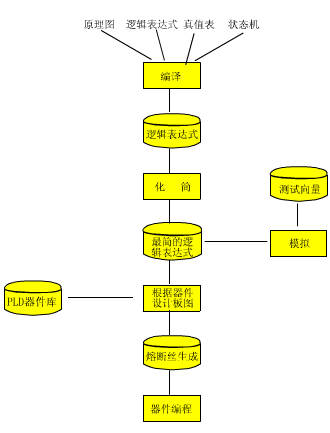

����2.����������ı�̼�ģ��

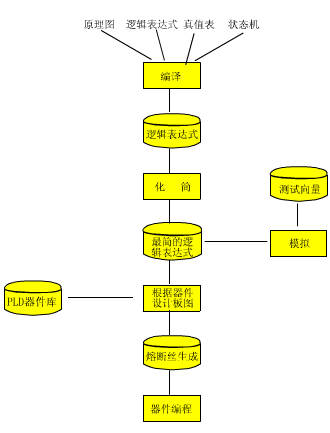

������������Ӳ������������������������ԭ��ͼ��������������ͨ�����������������б��룬��������ת��Ϊ��������IJ�����������ʽ����ͨ�������������ʽ�������������ٸ����������ص㽫����ʽ���������������������γ�PLD�������۶�˿�ļ���ͨ������JEDEC�ļ�,���ΪJED�ļ�����

����ͨ���ڽ��û���Ƶ������ص�����������ǰ��Ϊ�˼����ƵĽ���Ƿ���ȷ��ͨ������ͨ���������������ģ�⣬�������ƽ���Dz��������Ҫ�������

����3.ͨ���������JED�ļ����ص�PLD������

�������ϲ����γɵ��۶�˿�ļ��������ص�PLD������ȥ����ʵ����Ƶ�Ҫ���۶�˿�ļ�������һ����ͨ��������������ء�

�����������һ��ר�����ڶԿɱ��������EPROM,EEPROM,GAL,CPLD,PAL�ȣ����б�̵�רҵ�豸�������ı������̨����幫˾��ALLϵ�С��Ͼ������ع�˾��Superϵ�еȡ������ͨ��ͨ��������IJ��д�ӡ����JED�ļ����ص�������У�������ٽ�JED�ļ������������ص㽫��д�������ڲ����Ӷ��ﵽ���ص�Ŀ�ġ���ͼ������PLD����ƹ��̡�

2�� �ɱ����������������

�����ɱ�������������������ܶ࣬�����������Ҽ�һЩ������˾��������һϵ�е��������������������Щ�������ƶ��˿ɱ�������Ŀ��ٷ�չ��

����ͨ�����������ܵ�����������Ϊ������������ԭ��ͼ������������ࡣ��������DATA I/O��˾��BAEL���ԡ���ͨ��˾ASIC��ҵ�����������GAL������FM(Fast MAP)�����������������������������DATA I/O ��˾��Synario������Orcad��˾��PLD���������ڵ�·ͼ�������·ͼ����������������ƴ����������������Ҫ��DATA I/O ��˾��Synario����Ϊ��˵��GAL��������ƹ��̣�ͬʱ�����������Կ���Lattice��˾��pLSI������ispLSI�����ȡ�

����1.ABEL-HDL����

����ABEL-HDL������һ�����������������������ܵ�������ԣ������������������һ����һЩ�ؼ��ּ�һЩ�涨��

����(1)�����������ʾ

����ABEL-HDL��������ɷ�Ϊ��������������㡣������������ֱ��г�����������ķ��ż����ܣ���������к����Ϊʱ���·�вŻ�ʹ�õ���

ABEL-HDL�������������

| ����� |

���ȼ� |

���� |

���� |

���� |

| ! |

1 |

ȡ�� |

!(AB) |

(AB)�ķ� |

| & |

2 |

������ |

A&B |

A��B |

| # |

3 |

������ |

A#B |

A+B |

| $ |

4 |

������� |

A$B |

A��B |

| = |

|

��ֵ |

A=5 |

��5����A |

| == |

|

��ֵ��� |

A==1 |

�����ж���ֵ��� |

| != |

|

��ֵ���� |

A!=1 |

�����ж���ֵ���� |

ABEL-HDL���������������

| ����� |

���� |

���� |

���� |

| + |

������ |

C=A+B |

��A��B��ӣ������ٸ���C |

| - |

������ |

|

|

| * |

������ |

|

|

| / |

������ |

|

|

| <<,>> |

������λ |

A<<B |

��A����Bλ |

����(2)�ؼ���

| �ؼ��� |

�� ������ |

�١����� |

| module |

˵��ģ��Ŀ�ʼ����END��Ӧ |

MODULE tran |

| End |

ģ��Ľ��� |

END |

| Title |

˵��ģ������ƣ���ʡ�ԣ� |

Title 'U2 is a decode' |

| Equations |

������������صķ���ʽ�Ŀ�ʼ |

|

| Pin |

˵������I/O������ |

CLK,A Pin 1,2; |

| Istype |

˵������źŵ����� |

A Pin 19 istype 'COM'; |

| Test_vectors |

���������Ŀ�ʼ |

|

| Truth_table |

��ֵ���Ŀ�ʼ |

|

| When then Else |

��ʲôʱ���������������� |

When b then c=0 esle a=b |

| If then else |

|

|

����(3)ABEL������ƾ���

��������д��ȫ������ABEL-HDL���Ե�Դ�ļ���

�������������������·�����Ƿ�����ȫ�����ĵ�·�����ǿ�������ֵ����������ʽ����·ͼ�ȼ��ַ�ʽ�������������ܡ������ʽдΪ��

������Co=A��B+A��Ci+B��Ci

��λ�͵������S=A��B��C

������ֵ����дΪ��

| Ci |

A |

B |

Co |

S |

| 0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

1 |

| 0 |

1 |

0 |

0 |

1 |

| 0 |

1 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

0 |

| 1 |

1 |

0 |

1 |

0 |

| 1 |

1 |

1 |

1 |

1 |

������������ֵ���ͱ���ʽ�Կ��Ա�ʾ����ABEL��Դ�ļ����������ֱ��﷽ʽ��

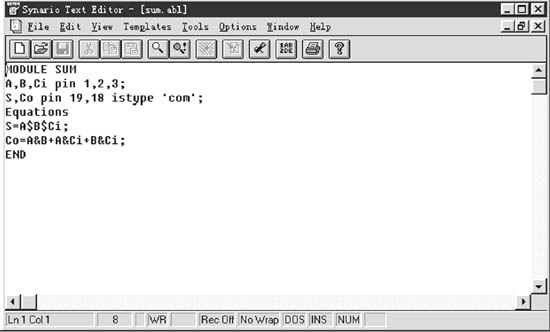

����Դ�ļ�1:�ñ���ʽ����ʾ

| Դ�ļ� |

��˵�������� |

| Module FSUM; |

ģ�鶨�壬FSUMΪģ������ÿ�н����÷ֺŽ��� |

| ����A,B,Ci pin 1,2,3; |

����A,B,Ci��Ӧ�ܽ�1,2,3 |

| ����S,Co pin 19,18 istype 'com'; |

����S,Co�Ĺܽţ���������Ϊ�������·��� |

| Equations |

��ʾ����һ��Ϊ������ʽ |

| ����S=A$B$Ci; |

|

| ����Co=A&B+A&Ci+B&Ci; |

|

| Test_vectors ([Ci,A,B]->[Co,S]) |

�����������壬����Ϊ������������ģ�������� |

| ��������������[0,0,0]->[0,0]; |

|

| ��������������[0,0,1]->[0,1]; |

|

| ��������������[0,1,0]->[0,1]; |

|

| ��������������[0,1,1]->[1,0]; |

|

| ��������������[1,0,0]->[0,1]; |

|

| ��������������[1,0,1]->[1,0]; |

|

| ��������������[1,1,0]->[1,0]; |

|

| ��������������[1,1,1]->[1,1]; |

|

| End |

ģ����� |

����Դ�ļ�2:����ֵ������ʾ

����ֻҪ�������Դ�ļ���Equations�������������һ�δ��漴�ɡ�

| Truth_table ([Ci,A,B]->[Co,S]) |

| ��������������[0,0,0]->[0,0]; |

| ��������������[0,0,1]->[0,1]; |

| ��������������[0,1,0]->[0,1]; |

| ��������������[0,1,1]->[1,0]; |

| ��������������[1,0,0]->[0,1]; |

| ��������������[1,0,1]->[1,0]; |

| ��������������[1,1,0]->[1,0]; |

| ��������������[1,1,1]->[1,1]; |

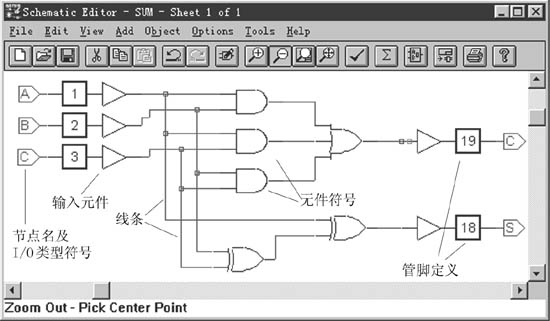

����2.ԭ��ͼ���뷨

����ABEL-HDL������Ϊһ�����������Կ��Խ���PLD����ƣ���������һЩ��·�Ѿ�����ͼֽ������ϣ����ֱ�ӽ�ԭ��ͼд��PLD��·��ȥ��ʡȥ���г�����Ƶ�ʱ�䣬���ż����ͼ�λ�����ķ�չ���������õ�·ͼ���������������������������ࡣ

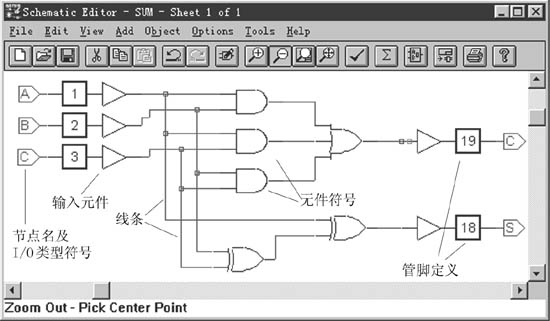

������ͼΪһ������ĵ�·ͼ����ͼ�Ͽɿ�����������¼������֣�

����

����(1)�����ţ��������DZ����ſ�ķ��ţ�Ҳ�����Ǵ���������·���ܵķ��ţ���ͼ�е�����š����ŷ��ţ���������������ŵĹ��ܣ����������ϳ�����Ӣ�Ƶķ��ţ����Զ���ʹ����Ӧ����ע�⣻

����(2)���ߣ��������Ӹ������ţ��书���൱��ʵ�ʵ�·�ĵ��ߣ�

����(3)I/O��־��������������ԭ��ͼ�����롢����źţ��źŵķ������롢�����˫�������룯����Ŷ�Ӧ���������źţ�

����(4)ͼƬ�����֣����ڰ���˵����·�Ĺ��ܣ����������·��ԭ������������·ԭ��û��ʵ�����塣 3�� �ɱ����������ƾ���

����1.��ABEL�������

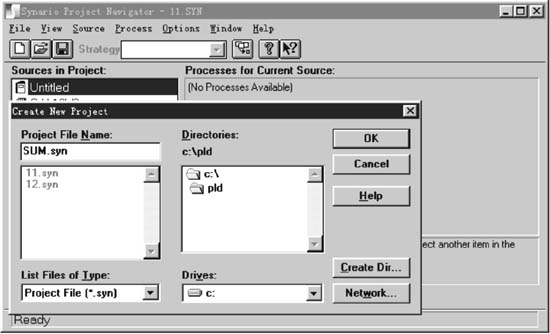

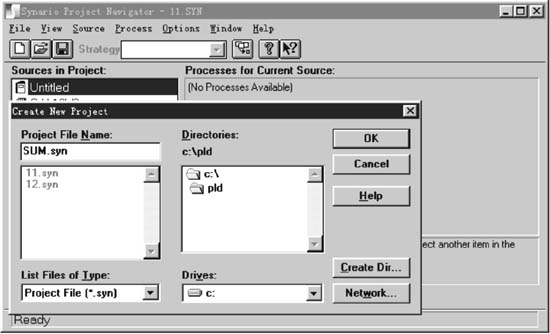

����(1)����Synario����������һ���µ������Ŀ

�� ��Windows 95�ij�������ִ��Synario,��Ļ�еij���Synario�����Ŀ�ʼ���档

�� �� File�˵���ѡ��New Profect��������µ���Ŀ����SUM������ͼ��ʾ��

������ʵ��ʹ��ʱӦע�����Ŀ������Ŀ¼λ�ã������˳���ǰ��������Ҳ���ǰ����ƣ���ǰ��Ŀ¼λ�ÿ�����ͼ���ҿ��п��Կ����������ע����ǣ��µ���Ŀ��һ�㲻Ҫʹ�����ĵ��ļ�����

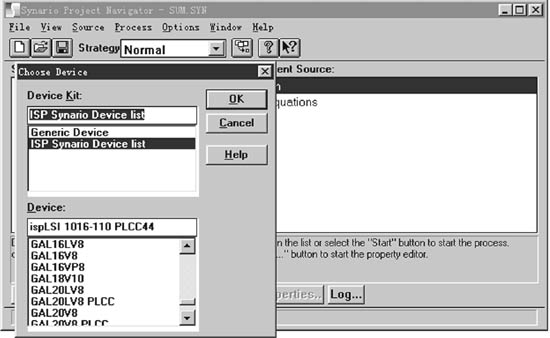

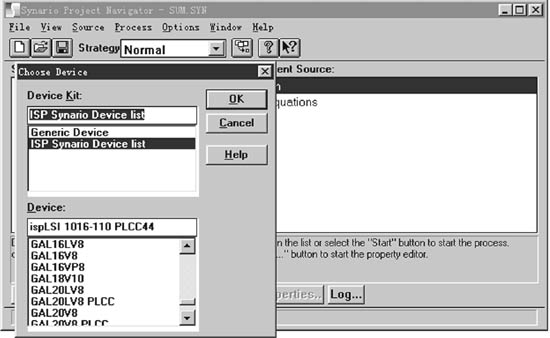

����(2)ѡ������

����˫��Virtual Device,������Choose Device�ĶԻ�������ͼ����Device Kit��ѡ��GAL16V8������OK��ťѡ�и�������

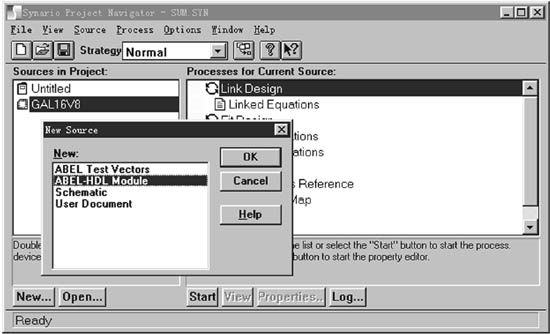

����(3)ѡ��Դ�ļ�������

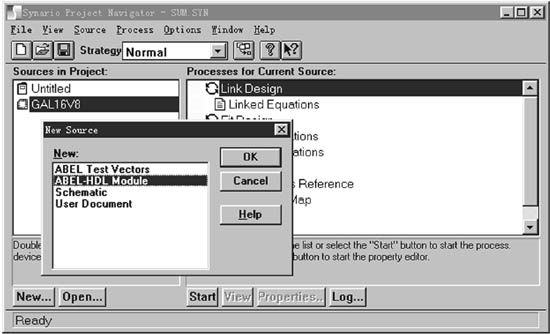

�����ɱ������Ƶ�Դ�ļ�������ABEL����Ҳ����ԭ��ͼ����Source�˵���ѡ��New������New�����ѡ��ABEL-Module��ʾ����ABEL���Ե�����,������Ӧ��ģ�������ļ���������ͼ��

�����������ע�⣬ABEL��ģ����������ʹ��������Ϊ�ļ��������������б��롣

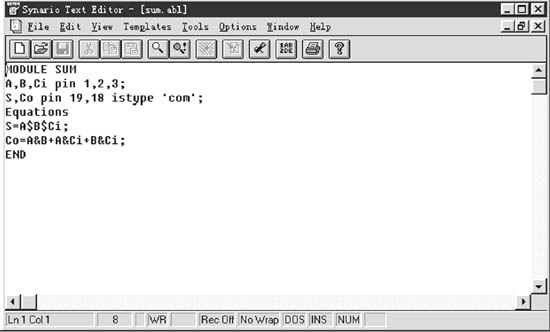

����(4)����ABEL����Դ���� �ڶ�Ӧ��Դ�ļ��༭����������Ӧ��Դ�ļ���������ʱ�ؼ��ֿ����Ǵ�д��Ҳ������Сд��ĸ���������Ĵ�Сд���ܸı䣬�����ڱ���ʱ������������ͼ��

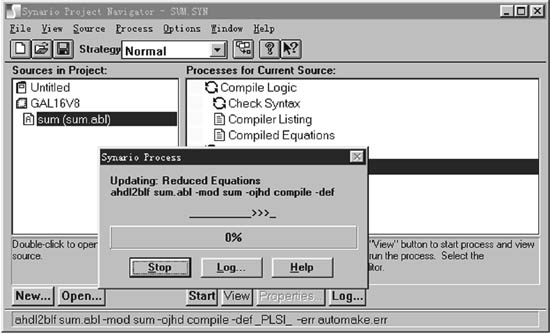

������(5)Դ�ļ�����

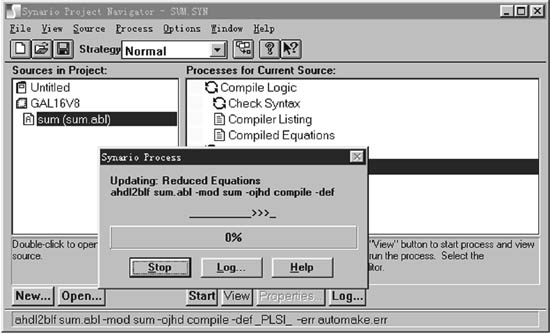

��������Ŀ�������£�ѡ����߷����ж�Ӧ��Դ�ļ����ļ�����˫���ұ������е�Reduce Logic���Կ�������ͼ��ʾ�ı�����̣���Դ�ļ���������������ո������뱨�棬˵����ɸ�������Ҫ����Դ����������������ʽ����Դ�ļ������������⣬���������˵�������ԭ�ط���

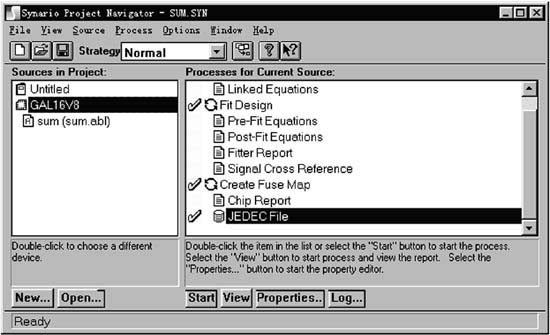

����(6)�۶�˿�ļ��γ�

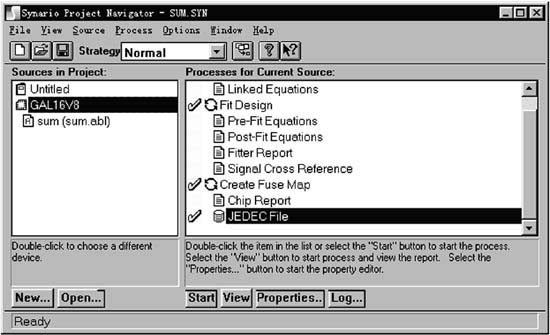

��������Ŀ��������ߵ�����ѡ��ʹ�õ�����(GAL16V8)��˫���ұ������е�Create Fuse Map, �ɿ�������ͼ��ʾ���۶�˿�ļ����γɹ��̣��籨��Ƶ�������Ҫ����ԴGAL16V8����ʵ�ֵĻ����������γ���չ��Ϊ.JED���۶�˿�ļ���

����(7)��������

���� JED���ļ������ص����е�GAL�����У�������������յ���ƣ�����JED�ļ���GAL����ר�ŵ�Ӳ����ƣ�����ר�ŵĵ��豸��ͨ�����ı�����������豸�������IJ��ڻ�������ͨ����Ӧ������JED�ļ����ص�GAL�����е�������ͼ������Super���������JED�ļ��Ļ��档

���� �����ñ������������ʱ������ѡ�������ij��ң���ͬ�ij�����������������ͬ����Ӧѡ���Ӧ���������ң����ѡ���������ͺţ���ʱ���Խ���Ҫ���ص�JED�ļ����뻺�����������������б�̣��������JED�ļ����غ��Զ�����һ��У�飬�������������������� �������ɸ�֪��������������˵��������

��������GAL������ʹ��CMOS�������������������ڶ�GAL�������ʱӦע��������������Ľӵ��Ƿ����ã�������Ա�������Ƿ�����硣

����2.ԭ��ͼ������Ʒ�

���� ԭ��ͼ���뷨��ʹ��ǰ�沽����ABEL������Ƶ�ǰ������ͬ��������ԭ��ͼ��ƵIJ��裺

����(1)ѡ��Դ�ļ�������ѡ��Schematic�������Ӧ��ͼ���ļ���������ͼ��ʾ��ԭ��ͼ������档

����(2)����Ԫ����ѡ���Add�е�Symbol�����Ļ����Symbol Libraries�Ի���ѡ����Ҫ�ļ������У��� GATE�����ŵ�·��ARITHS����ѧ����Ԫ����IOPAD���������Ԫ����MUXEX����·ѡ�� ��REGS���Ĵ�����

����(3)������Ԫ������Add�˵���ѡ��Wire����MOUSE����������Ӵ��������϶�MOUSE����һ���ٵ����ͽ������������ˡ�

����(4)�������������������/���Ԫ�����ڲ˵�Add��ѡ��Symbol�е�IOPADԪ�����ڵ�·������/�������IOPADԪ����

����(5)���ӿ�����˸�������Add�˵���ѡ��Net Name�����Ļ�ײ������������������������س�����������ճ�ڹ������MOUSEһ���ƶ���������Ƶ����������˵������������ͱ� ����������/�������

����(6)���ӿڵ���������˱�ע���ͣ���Add�˵���ѡ��I/O Markers�����Ӧ�����������������������ı�ǡ�

����(7)�����������ܽţ���Add��ѡ��Symbol Attribute��MOUSE����Ƶ���������˵�IOPAD�ϵ�������SynarioPin=*�е�*��Ϊ���������ܽźš�

���� ����һ��������ԭ��ͼ�Ѿ�������ϣ�����·ͼ������˳���Ϳ�����ABEL_HDL����һ�����б��룬���տ���JED�ļ��� |

Alexa

Alexa mcusy_cn#126.com (���#�ij�@)

mcusy_cn#126.com (���#�ij�@)  ������522422171

������522422171 51/AVR��Ƭ��������վ�� <

51/AVR��Ƭ��������վ�� <

��������

��������