摘 要: 针对重要系统可靠性要求,特设计了一种双CPU控制系统。在该系统中,两个CPU彼此独立运行,可以自动或手动实现双机的主辅切换,只有主CPU能正常读写外部RAM数据和控制输出。

关键词 双CPU 切换 监控 控制

单片微机具有小巧灵活、易扩展成为功能强大的控制系统。目前,一些监控终端以及许多独立的控制系统(如:发电机的微机励磁装置)多以单片微机为核心构成。但由于诸如工作环境恶劣、电磁干扰等原因,即使使用按工业测控环境要求设计的单片微机也难以保证控制系统能长期可靠的运行,从而导致控制系统瘫痪。这样,如何提高控制系统的可靠性,保证测控系统能正确稳定的运行就尤为重要。显然,采用双CPU冗余设计是非常有效的一种解决办法。由于单片微机的功能强大,价格低廉,为设计双机冗余系统提供了很好的条件。为此,我们设计了一种由两片单片微机组成的双机容错系统,以比较简单和与传统的多CPU系统完全不同思路的设计方法实现了双机的互为备用及相互切换。在该双机冗余系统设计中,其关键问题是双机系统的重构策略和双机系统的仲裁逻辑切换。

1 传统的多CPU系统设计方法

传统的多CPU系统的常用设计方法有三种:

① 利用双口RAM实现CPU之间的通信。双口RAM是一种高速的并行传输芯片,具有两套I/O口和竞争裁决电路,可以同时联接两个CPU,这样通过双口RAM可以实现多CPU之间通信。

② 利用共享内存的方法实现CPU之间的通信。这种方法与上一种方法类似,所不同的是,上一种方法是利用双口RAM的竞争裁决电路实现对RAM的访问,而这种方法是利用不同的时序实现内存共享的。

③ 利用总线方法实现CPU之间的通信。通过接口芯片或CPU本身具备的SPI、I2C以及SMBus等接口实现CPU之间的通信。

2 该双CPU系统的结构和工作原理

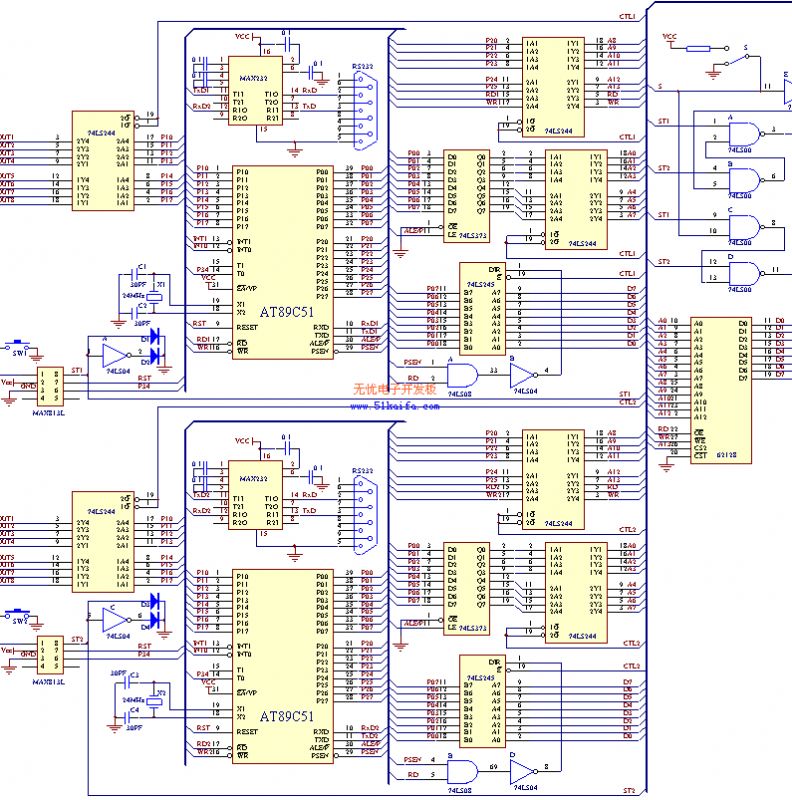

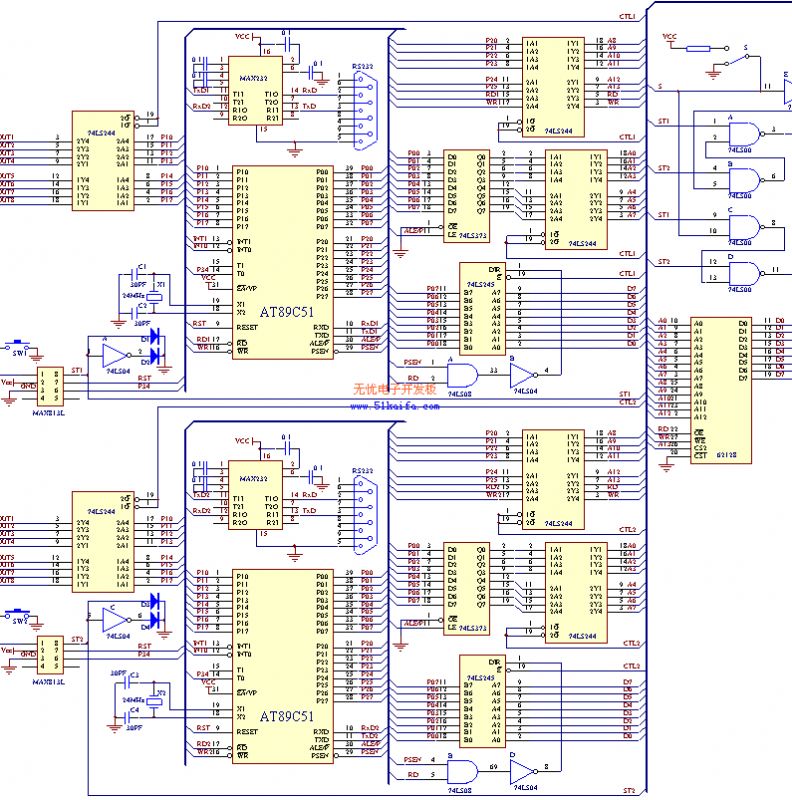

该双CPU控制系统与传统的多CPU系统的设计方法完全不同,它由两片Atmel公司生产的AT89C51 CPU构成,双机互为备用,彼此独立并行运行,硬逻辑切换。其双CPU控制系统原理框图如图1所示。

这是一种非表决式的双机冗余系统,一个CPU 作为另一CPU的热备份 ,双机在任务上同步运行。所有输入信号通过输入接口同时送给两个CPU,但CPU 运算、处理后的输出量受到仲裁切换电路的控制,只有主CPU允许读写外部数据存贮器及输出至外部设备,当主CPU发生故障时,系统的自我检测切换逻辑将发出信号,自动切断其输出通道,并通过CPU的工作指示系统报警。此时,系统或自动或人工切换到另一个备用的CPU,并同时打开其输出通道,备用机变为主机运行状态,控制系统这时降级为单机运行。人们可以将原主机拔离系统以便进行维修。从图中可知,两个CPU的地址、数据及控制总线都通过一组三态门(三态门1、2)输出与外部数据存贮器相接,两个CPU的某些输出控制I/O口都通过另一组三态门(三态门3、4)输出与外部输出控制设备相接,两组三态门的控制端都同时受仲裁切换电路控制,而仲裁切换电路的两路输出互为反逻辑,即只有一路输出能使所控制的对应三态门(如三态门1、3)正常输出,另一路输出使所控制的对应三态门(如三态门2、4)处于高阻状态,从而不影响主CPU正常读写数据和向控制I/O口输出数据。

图1 双CPU控制系统原理框图

|

表1 双机仲裁切换逻辑真值表

|

ST1 ST2 |

S |

CTL1 CTL2 |

CPU1 CPU2 |

|

1 1 |

1

0 |

0 1

1 0 |

主 辅

辅 主 |

|

0 0 |

´ |

1 1 |

两CPU均工作不正常 |

|

1 0 |

´ |

0 1 |

CPU1为主机,CPU2工作不正常 |

|

0 1 |

´ |

1 0 |

CPU2为主机,CPU1工作不正常 |

|

3 双机仲裁切换逻辑电路

在该双CPU控制系统中,两者互为热备份,同时运行,一台为主机,另一台为备份机。在双CPU都正常运行的情况下,系统默认CPU1为主机, CPU2为备份机。当主机出现故障时,要求系统能自动切换到备份机,使备份机提升成为主机,从而代替原主机从故障发生处连续运行并发出报警信号。同时要求能通过手动开关人为选定主机运行。设判别两个CPU是否正常工作的信号分别为ST1、ST2,工作正常时它们的状态为1,工作不正常时状态为0。仲裁切换电路输出为0的控制端控制工作正常的CPU的相应三态门组使能,仲裁切换电路输出为1的控制端控制另一CPU的相应三态门组禁止输出。自动或手动选择主机的控制开关为S,当两个CPU都工作正常时,可通过S开关自动选择或指定主机(当S开关状态为1时为自动默认CPU1为主机,当S开关状态为0时则强制CPU2为主机);当两个CPU中任意一个工作不正常时,则此时与S开关的状态无关,仲裁切换电路的输出能确保只有与工作正常的CPU相连的三态门组的使能端为0,从而控制该正常CPU正常读写数据和输出控制;当两个CPU都不正常时,仲裁切换电路的两个输出都为1,两个CPU都不能正常读写数据和输出控制。这样当两个CPU中任何一个或全正常时就能保证只有一个CPU能正常读写数据和输出控制,当两个CPU都不正常时,则理所当然系统不能正常工作。按要求可得真值表如表1所示。

由真值表可得仲裁切换电路的两路控制三态门的控制信号逻辑CTL1、CTL2分别为:

,

,

构成的仲裁切换电路如图2所示。

4 CPU状态监控电路

监控电路采用了具有电源监控电路和看门狗功能的微处理芯片MAX813L,该芯片它具有4个功能:

① 看门狗计时器功能。当看门狗输入信号在1.6s内无变化时,产生看门狗输出;

② 电压监控功能。当掉电或电源监测电压低于1.25V时,产生掉电输出;

③ 上电复位功能。当上电时自动产生脉宽200ms的复位信号;

④ 人工复位功能。当人工复位端输入低电平时,产生复位信号输出。

MAX813L采用DIP-8封装,如图3所示,引脚功能说明如下:

① MR:手工复位输入端,可接人工复位按钮,该端输入低电平保持140ms以上,可产生复位(RST)信号;

② Vcc:+5v电源;

③ GND:电源地;

④ PFI:电源检测输入端;

⑤ PFO:电源检测输出端,电源正常时,保持高电平;

⑥ WDI:看门狗输入端。俗称“喂狗”信号,必须在1.6s内使该端输入反向信号;

⑦ RST:复位输出端。高电平有效,可输出200ms的正脉冲,当电源Vcc低于4.65v时,RST保持高电平;

⑧ WDO:看门狗输出端。正常工作时输出高电平,当WDI信号在1.6s内不能及时送入并反向时,该端输出低电平信号。

因AT89C51无看门狗功能,为了监测系统状态,在本系统中主要利用的是MAX813L的看门狗计时器功能。其中看门狗输入端WDI由CPU的P3.4提供,CPU在规定的时间内定时改变P3.4

的状态,由看门狗输出端WDO提供当前CPU的状态信号至仲裁切换电路的STi(i =1或2)端,从而由仲裁切换电路自动或手动确定主机。图4为用MAX813L为CPU1接的看门狗电路,当CPU1工作正常时能正常提供P3.4信号则WDO端ST1输出高电平,D1亮D2灭;当CPU1工作不正常时不能正常提供P3.4信号则WDO端ST1输出低电平,D2亮D1灭。

5 系统硬件电路

图5为利用本文介绍的双CPU的切换及控制系统组成的一种硬件电路。从图中可知,系统每个CPU都可以通过RS232串行口与上位机通信,两片CPU彼此独立运行,通过双机仲裁切换逻辑电路共享外部16KB RAM和控制8路I/O口输出。利用这种方法还可以通过增加三态门组成更大容量(最大64KB)的外部RAM和更多的输出控制I/O口或扩展I/O口。

图5 一种双CPU的切换及控制系统的硬件电路

6 结束语

该双CPU控制系统构思独特,两个CPU彼此独立运行,但读写的都是同一块外部RAM的数据,只是只有主CPU能实际读写数据,故不存在内存数据交换和共享问题,同时也只有主CPU能输出控制外部设备,可广泛应用于要求高可靠性控制的场合,作者将该项技术应用到自行研制的电脑样板切割机上取得了较满意的结果。

Alexa

Alexa mcusy_cn#126.com (请把#改成@)

mcusy_cn#126.com (请把#改成@)  交流:522422171

交流:522422171 51/AVR单片机技术驿站! <

51/AVR单片机技术驿站! <

,

,

最新评论

最新评论