作者:李忠桥 游小杰 郑琼林 来源:单片机与嵌入式系统应用

摘要 详细介绍串行同步通信的特点,说明如何通过硬件设计和软件纠错来确保数据流的同步;给出一种纠正数据偏移的方法,并以数字信号处理器TMS320LF2407A与单片机MsP430F135之间的SPI通信为例进行说明。

关键词 SPI 串行同步通信 MSP430F135 TMS320LF2407A

SPI是串行外设接口(Serial Peripheral Intcrface)的缩写,通常称为“同步外设接口”,是由Motorola公司开发的全双工同步串行总线。该总线大量用在微处理器及其外设器件的通信中。与SPI有关的软件设计比较简单,使CPU有更多的时间处理其他事务。现在,越来越多的单片机带有SPI,采用SPI的外围芯片也与日俱增。采用 SPI通信可以简化电路设计.提高电路可靠性,降低系统成本。

1 SPI通信的基本方式

SPI通信总线定义了以下4个接口信号。

◇SIMO:从入/主出。

◇SOMI:从出/主入。

◇SCK:串行时钟。

◇SS:从届选择(在有些芯片中定义为STE信号)。

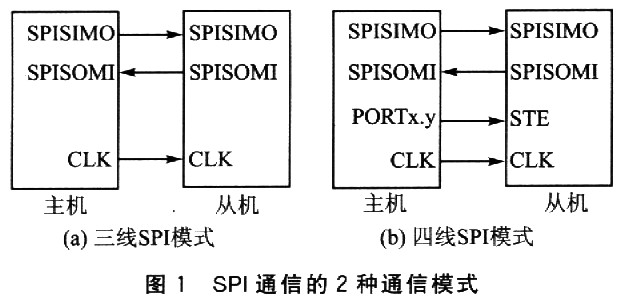

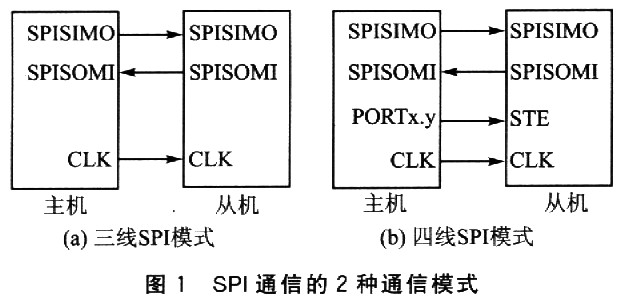

SPI通信有三线SPI和四线SPI两种模式。在三线SPI模式下,从属选择信号SS/STE不起作用;采用四线SPI模式时,SS/STE信号为高电平时禁止从机接收和发送数据,SS/STE信号为低电平时允许从机接收和发送数据。SPI通信足一种基于主一从配置的通信,提供串行时钟信号的―方是主机,其他的为从机。图l为2种通信模式下2台单片机之间的连接图。如果一个系统中有多台从机,那么主机就要为每一台从机提供一个从属选择信号,以确保任一时刻只有一台从机起作用。

在SPI通信中,数据是同步发送和接收的。在串行时钟信号的作用下,主机在通过SIMO信号线发送数据的同时,也在通过SOMI信号线接收从机发送的数据;从机在通过SIMO信号线接收数据的同时,也在通过SOMI信号线向主机发送数据。Motorola公司没有定义任何通用SPT的时钟规范,但是所有具有SPI功能的单片机中,都可以通过设置相应的寄存器来设置时钟极性和时钟相位。对时钟极性的设置决定了静止时 SPI串行时钟的有效状态,而对时钟相位的设置则规定了处理器在何时发送和接收数据。之所以如此,是为了适应不同外设和线路的需要,因为有些外设在时钟信号的上升滑锁存数据,而有些外设则在时钟信号的下降沿锁存数据。

SPI传输串行数据时,首先传输数据的最高位。波特率可以达到几Mbps,实际速度不仅取决于SPI硬件,而且还受到软件设计的约束。

2 数据流的同步

同步串行通信的基本特点是:同步串行通信是以字符块为信息单位传送的,而每帧信息包含成百上千个字符,因此,数据传送一旦开始,就要求每帧信息内部的每一位都要同步。也就是说,不仅字符内部的位传送是同步的,而且字符与字符之间的传送也必须是同步的,这样才能保证收/发双方对每一位都同步。显然,这种通信方式对时钟同步要求非常严格。为此,收/发两端必须使用同一时钟来控制数据块传输中字符与字符、字符内部位与位之间的同步。

不论以何种方式进行通信,都必须制定一个通信协议。SPI通信也不例外。通信协议通常可以被分为3个部分:语法、语义和定时关系。这3部分分别规定了通信双方“如何讲”、“讲什么”以及“何时讲”的问题。

同步通信的通信协议比较简单。通常在数据块的前面冠以同步字符,在数据块的结尾加上差错控制字符就构成了同步通信的一帧数据。通过选择工作模式,设置波特率、时钟极性和相位以及软件的设计,就可以实现数据流的同步。

在双机或一台单片机与一片外围芯片的SPl通信中常选择三线模式}而在多方SPI通信中则通常使用四线SPI模式,这时SS/STE信号线用来对从机进行选择。在一主多从的SPI通信中,主机必须为每一台从机或外围芯片提供一个SS/STE信号。使得任一时刻只有一台从机或外围芯片起作用。如果所有的从机都只从主机接收数据,而不向主机发送数据,那么也可以使用三线SPI模式。SS/STE信号也可以用来对主机进行选择,不过通信将变得很复杂。选择正确的工作模式是进行可靠的SPI通信的前提。

SPI通信是在主机提供的时钟信号驱动下进行的,设置波特率就是设置主机提供的时钟信号的频率。因此,波特率的设置就显得相当重要。需要多方考虑。单片机与其外围器件进行通信时,一次可能只发送1个或2个字节的数据,可以把波特率设得高一些,只要不超过硬件允许的范围即可。如果是两台单片机之间进行通信,那么每次传送的往往是一组数据,否则就失去了同步通信的意义。这种情况下,就必须考虑接收数据一方的运行速度。因为无论是采用查询还是中断方式接收数据,每收到1个字节或1个字的数据后,接收方的单片机就必须从接收缓冲寄存器中取一次数据。这个过程必须在下一个字节或字传送完毕前结束。也就是说,处理时间不能超过8个或16个串行时钟周期;否则,将会发生溢出错误。例如,完成这个过程需要4μs,当接收缓冲寄存器为8位时,串行时钟的波特率就不能超过2 Mbps;当接收缓冲寄存器为16位时,串行时钟的波特率就不能超过4 Mbps。有的单片机片内RAM有限,没有足够的RAM空间用来保存中间数据,每收到1个字节或字的数据就必须处理一次。这样一来,串行时钟的波特率就需要设置得更低。

当单片机与其外围芯片进行SPI通信时,应当根据外围芯片的时序来设置串行时钟的极性和相位。例如,某芯片在时钟信号的上升沿接收SPI线上的数据,那么主机就必须采用无延时的下降沿或有延时的上升沿时钟方式来发送SPI数据。当两台单片机之间进行SPI通信时,双方对时钟信号极性和相位的设置必须相同。

在硬件连接方面,需要引起注意的问题是上电复位后引脚SS/STE上信号的极性。如果上电复位后,引脚SS/STE上为低电平,则有可能收到1位伪数据。在四线SPI模式下,如果在从机的SS/STE引脚上接一个上拉电阻,就可以避免这种情况的发生。

如果在通信过程中,出现串行时钟信号丢失或干扰,将造成数据流的不同步,通信的各方就收不到正确的数据。所渭“数据流不同步”是指数据的比特位发生了偏移。例如,发送的数据是0xA9和0x36,但是收到的却是Ox52和0x6C,数据向右移了一位。一旦发生这种错误,仅靠硬件是无法纠正的,若不在软件中采取措施,则将一直错下去,永远收不到正确的数据。

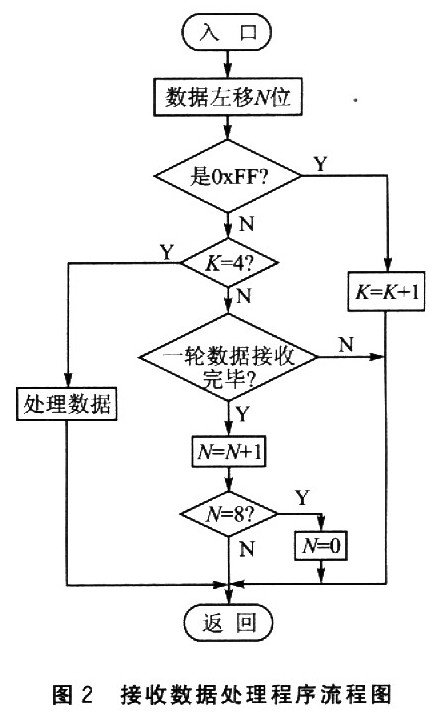

采用软件纠错的关键在于找出偏移的位数,然后据此采取措施,得到正确的结果。一般说来,在通信数据中包含了一些特殊字符,用于标志数据流的开始和终止。处理数据时,首先寻找这些特殊字符。如果不能发现这些特殊字符,就说明数据发生了偏移,需要进行纠错处理。具体的处理办法如下:假设数据以字节为单位,用前一个数据的后N位和后一个数据的前(8-N)位重新组成一个新的数据。其中,1≤N≤7。改变N的值,直到从重组的数据中发现特殊字符为止。此时的N值就是数据流发生偏移的位数,然后根据这个值对所收到的其他数据进行重组,就可以得到正确的结果。与此同时,如果还要发送数据,就要对发送出去的数据进行类似的处理。因为如果通信的一方收到的数据发生偏移,那么另一方收到的数据肯定也发生了相同的偏移。

通常要求系统上电复位后,从机先于主机开始工作。如果从机在主机之后开始工作,就有可能丢掉部分时钟信号,使得从机并不是从数据的第一位开始接收,造成数据流的不同步。可通过硬件延时或软件延时的方法,来确保从机先于主机工作。

3 实例

现在以数字信号处理器TMS320LF2407A和单片机MSP430F135为例,说明如何确保SPI通信中数据流的同步。这里采用三线SPI模式, TMS320LF2407A设置为主机,MSP430F135设置为从机;双方的时钟极性和相位都设置为无延时的上升沿。TMS320LF2407A的主频为40 MHz,采用定时发送/接收数据的方式工作,每间隔800μs发送一个字节,波特率为200 kHz。这样设置的原因是,MSP430F135的主频为8 MHz,片内的RAM只有512字节,没有足够的RAM用于保存中间数据,每接收一个字节就得进行一次处理,所以必须留有足够的时间给 MSP430F135进行数据的处理。每一轮发送132字节,由4个引导字符0xFF加上128字节的数据组成。MSP430F135采用中断的方式接收/发送数据。

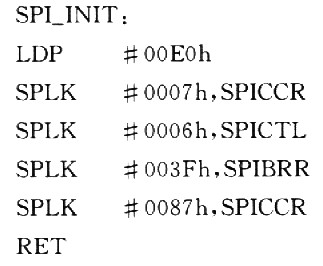

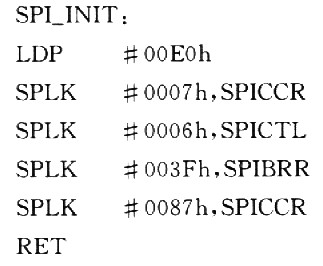

以下是用汇编语言编写的TMS320LF2407A的SPI通信初始化子程序:

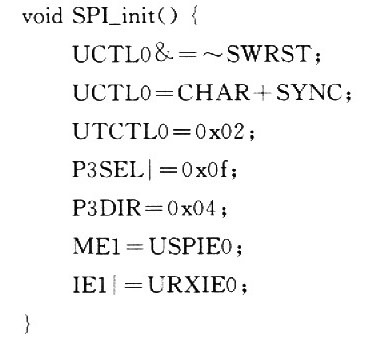

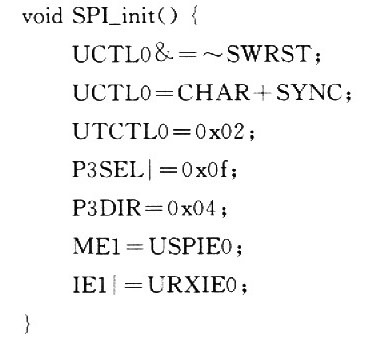

下面是用C语言编写的MSP430F135的SPI通信初始化子程序:

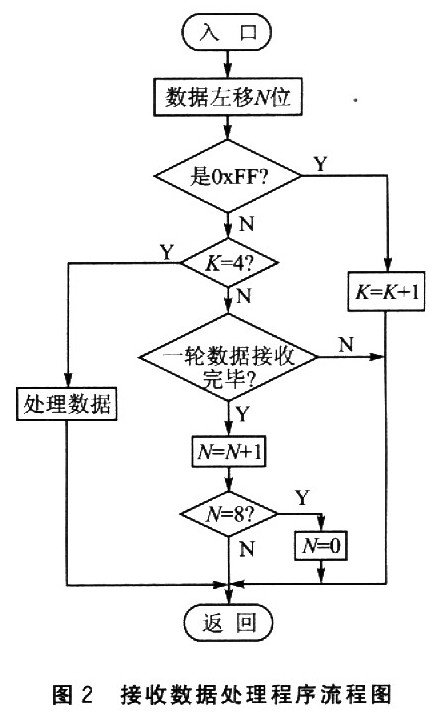

在MSP430F135的接收数据处理程序中还包含了防止数据流发生偏移的措施,实现方法与前文所述相同。图2是接收数据处理程序的流程图。

上述程序是电镀用开关电源控制程序的一部分。DSP控制器TMS320LF2407A负责主电路的控制;单片机 MSP430F135作为辅助控制器,负责键盘和液晶显示器的控制。两个微控制器之间通过SPI通信交换信息。实际应用表明,采用这种方法进行SPI通信是可靠的。

4 结论

SPI通信具有硬件连接简单、使用方便等优点。采取硬件和软件相结合的措施,可以确保 SPI通信中数据流的同步,实现可靠通信。通过电镀用开关电源中数字信号处理器TMS320LF2407A和MSP430F135单片机之间SPI通信的实例,验证了文中提出的三线模式SPI通信中,防止和纠正比特位发生偏移的方法的有效性。

Alexa

Alexa mcusy_cn#126.com (请把#改成@)

mcusy_cn#126.com (请把#改成@)  交流:522422171

交流:522422171 51/AVR单片机技术驿站! <

51/AVR单片机技术驿站! <

最新评论

最新评论