|

数据选择器又称为多路选择器(Multiplexer)是一种多个输入一个输出的中规模器件,其输出的信号在某一时刻仅与输入端信号的一路信号相同,即输出为输入端信号中选择一个输出。

我们在日常生活中常常会碰到这种多路选择器的情况,如家庭音响系统中在选择音源时,可以在CD、录音磁带、收音机中选择一路进行欣赏,这是将多个信号源中选择一路进行输出,但这例子中的信号是模拟信号,而这里主要讲的是数据信号。

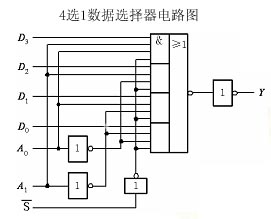

1、数据选择器的电路结构

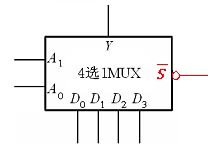

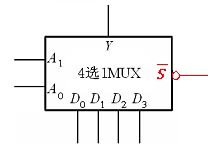

数据选择器在上面已经讲到是在多个输入中选择一路进行输出,至于选择哪一路,须首先对输入信号进行编号,另外还须一个选择哪一路输入的选择信号,于是我们可得到如下图的4输入的多路选择器的框图,下表列出了其工作的情况。

|

/S |

A1 |

A0 |

Y |

|

0 |

0 |

0 |

D0 |

|

0 |

0 |

1 |

D1 |

|

0 |

1 |

1 |

D2 |

|

0 |

1 |

1 |

D3 |

|

1 |

× |

× |

0 |

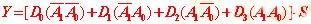

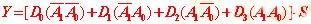

对上面真值表的分析不难写出输出与输入的关系为:

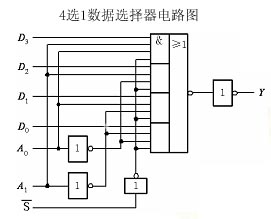

由上式可画出下图所示的多路选择器的内部电路,其左图为基本的电路形式,右图加上了一个使能端,当其为高电平时,输出始终为高电平,仅当其为低电平,其输出才满足上式的功能。

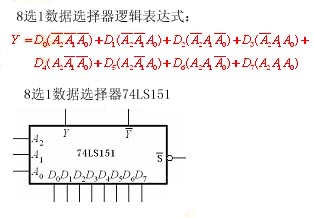

2、标准中规模数据选择器

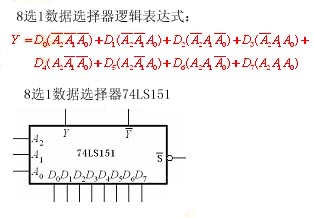

常见标准中规模数据选择器有74153(双4选1多路选择器)、74151A(8选1多路选择器)、74150(16选1多路选择器),这里以74151A为例说明其结构及逻辑功能。下图为74151A的逻辑符号。

| 地 址 输 入 |

输 出 |

| A2 |

A1 |

A0 |

/ST |

Y |

/Y |

| × |

× |

× |

1 |

0 |

1 |

| 0 |

0 |

0 |

0 |

D0 |

/D0 |

| 0 |

0 |

1 |

0 |

D1 |

/D1 |

| 0 |

1 |

0 |

0 |

D2 |

/D2 |

| 0 |

1 |

1 |

0 |

D3 |

/D3 |

| 1 |

0 |

0 |

0 |

D4 |

/D4 |

| 1 |

0 |

1 |

0 |

D5 |

/D5 |

| 1 |

1 |

0 |

0 |

D6 |

/D6 |

| 1 |

1 |

1 |

0 |

D7 |

/D7 |

3、数据选择器组合逻辑电路

从数据选择器的输出与输入的表达式中可以看出,其实际上是数据输入与地址输入的最小项相与的关系,所以数据选择器可以实现各种组合逻辑功能。

|

Alexa

Alexa mcusy_cn#126.com (请把#改成@)

mcusy_cn#126.com (请把#改成@)  交流:522422171

交流:522422171 51/AVR单片机技术驿站! <

51/AVR单片机技术驿站! <

最新评论

最新评论