|

译码器是组合逻辑电路的一个重要的器件,其可以分为:变量译码和显示译码两类。

变量译码一般是一种较少输入变为较多输出的器件,一般分为2n译码和8421BCD码译码两类。

显示译码主要解决二进制数显示成对应的十、或十六进制数的转换功能,一般其可分为驱动LED和驱动LCD两类。 变量译码

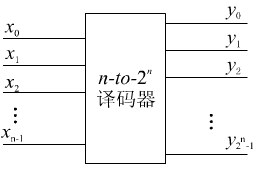

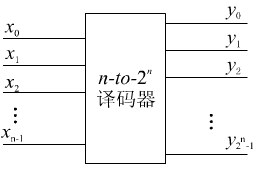

变量译码器是一个将n个输入变为2n个输出的多输出端的组合逻辑电路。其模型可用下图来表示,其是输入变化的所有组合中,每个输出为1的情况仅一次,由于最小项在真值表中仅有一次为1,所以输出端为输入变量的最小项的组合。故译码器又可以称为最小项发生器电路。

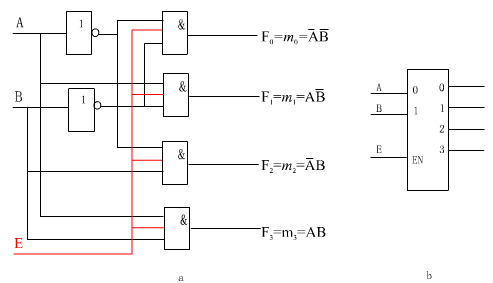

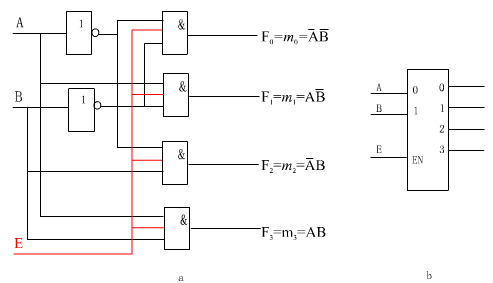

1、译码器电路结构

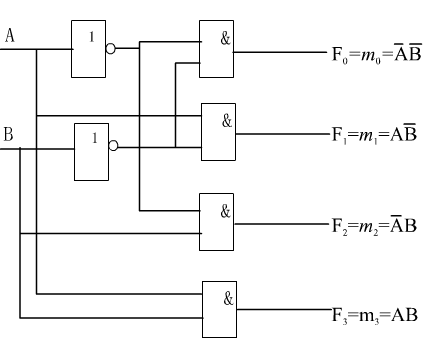

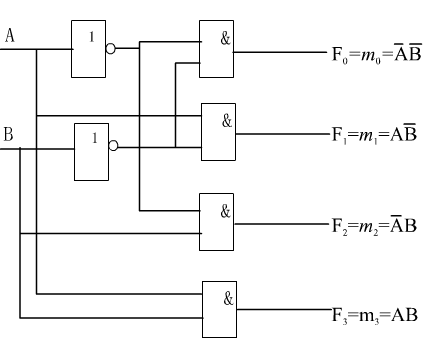

在讨论译码器的功能前我们来看一下译码器的内部结构,下图是一个主要由与门电路构成的2输入译码器,其输出共有22个(即4),从图上可以每个其输出对应于一个最小项。在这电路中当输入BA的取值为10,即对应于十进制数的2时,其F2输出为高电平,其余的输出为0。

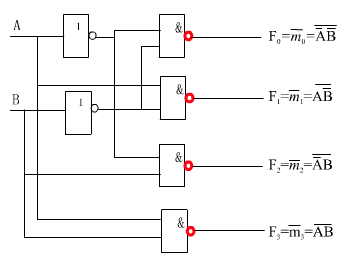

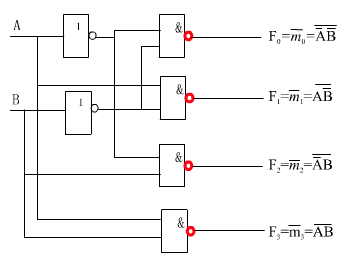

下图同样是一个2输入的译码器,但由于其主要使用了与非门构成的,其每个输出对应于一个最小项的非。在这电路中,当输入BA的取会为10时,其输出F2不再为1,而是输出为0,其余的输出为1。

我们将下面这种译码器电路看作输出低电平有效(即当输入变量对应于十进制i时,其对应的第i个输出端为低电平,其余为高电平)。而前面的译码器当然就是高电平有效了。

上面列出的两个电路为2输入的情况,对于输入为2个以上的情况也与此相同,同样可以有输出高电平有效的,也有输出低电平有效的。

2、用译码器实现逻辑功能

由于任何一组合逻辑电路都可以写成最小项表达式的形式,而译码器电路的输出列出了该电路的所有最小项表达式(或最小项的非表达式),故我们可能用译码器电路实现各种组合逻辑电路。

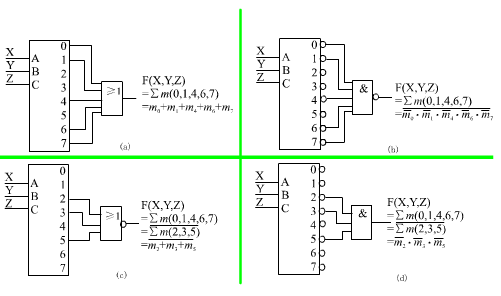

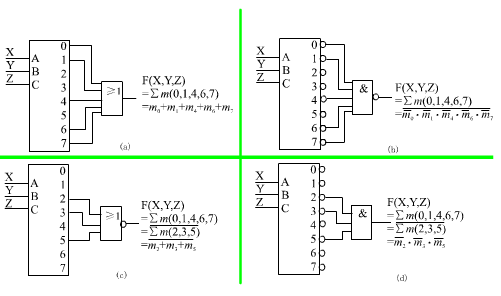

例 用译码电路实现F(X,Y,Z)=∑(0,1,4,6,7)=∏M(2,3,5)

我们实现该逻辑功能可以有几种方法,下图列出了四种方法,从这四个图中你应可以总结出其规律。

其中:

图a为高电平有较输出加或门的实现方法;

图b为低电平有较输出加与非门的实现方法;

图c为高电平有较输出加或非门的实现方法;

图d为低电平有较输出加与非门的实现方法;

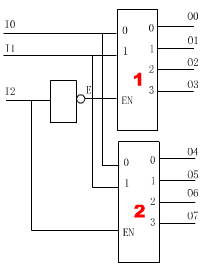

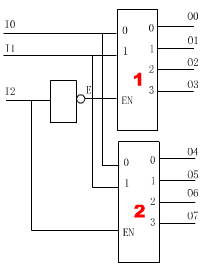

3、使能输入端(Enable Inputs)

在中规模集成电路中经常会碰到使能端(Enable Pin),使能端可以是输入,也可以是输出,其是用来扩展中规模集成电路功能的输入/输出端,下图a是一个2输入译码器上加上一个输入E,由于输入端E的加入,其功能发生了变化,当E=0时,其输出全部为0,而该译码器在没有加上E端时,其为高电平有效,这时其输出端没有一个处于有效工作状态,我们可以理解为E=0时,该译码器不工作;当E=1时,我们看到,其译码器可以正常工作,我们把这种输入端在E=1时能正常工作的使能端叫做高电平有效。下图b为其简化的逻辑符号。

下图是使用使能端将两个2输入的译码器转变为3输入的译码器的例子,在下图中当I2为低电平时,第1个译码器的使能端为高电平,其正常工作,而第2个译码器此时不工作,于是译码器1的输出对应于输入I3I2I1的0~3;当I2为高电平时,译码器2工作,而译码器1不工作,故其输出对应于输入I2I1I0的4~7,故下图电路实现了利用使能端将2输入的译码器扩展为3输入的译码器。

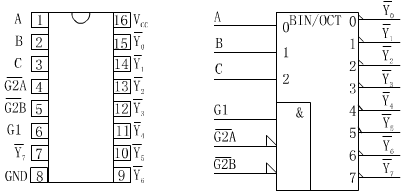

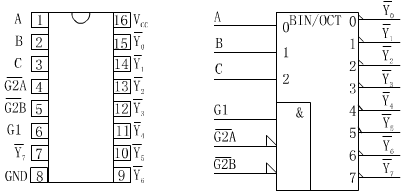

4、标准中规模译码器电路

在中规模集成电路中译码器有几种型号,使用最广的通常是74138,其是一个3到8的译码器,下图是其逻辑符号及管脚排布,下表中列出了该器件的逻辑功能,从表中可以看出其输出为低电平有效,使能端G1为高电平有效,/G2,/G3为低电平有效,当其中一个为低电平,输出端全部为1。

| 输 入 |

输 出 |

| 使能端 |

选 择 端 |

| G1 |

/G2* |

C |

B |

A |

/Y0 |

/Y1 |

/Y2 |

/Y3 |

/Y4 |

/Y5 |

/Y6 |

/Y7 |

| 1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

| 1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

| 1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

| 1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

| 1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

| × |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| /G2*=/G1A+/G2B |

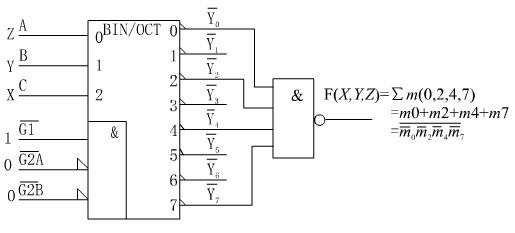

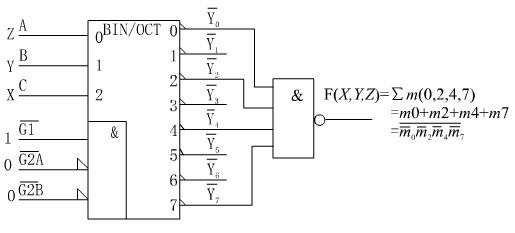

例 试用74138实现函数F(X,Y,Z)=∑m(0,2,4,7)

用74138实现函数与前面讲到的译码器实现逻辑函数的方法相同,但须注意两点:

1.74138的输出是低电平有效,故实现逻辑功能时,输出端不可接或门及或非门(因为每次仅一个为低电平,其余皆为高电平);

2.74138与前面不同的是,其有使能端,故使能端必须加以处理,否则无法实现需要的逻辑功能。下图给出了其最终的电路。

显示译码

5、常用的显示器件工作原理

在数字系统中常见的数码显示器通常有:发光二极管数码管(LED数码管)和液晶显示数码管(LCD数码管)两种。发光二极管数码管是用发光二极管构成显示数码的笔划来显示数字,由于发二极管会发光,故LED数码管适用于各种场合。液晶显示数码管是利用液晶材料在交变电压的作用下晶体材料会吸收光线,而没有交变电场作用下有笔划不会听吸光,这样就可以来显示数码,但由于液晶材料须有光时才能使用,故不能用于无外界光的场合(现在便携式电脑的液晶显示器是用背光灯的作用下可以在夜间使用),但液晶显示器有一个最大的优点就是耗电相当节省,所以广泛使用于小型计算器等小型设备的数码显示。

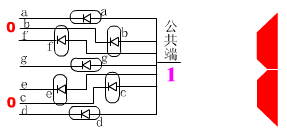

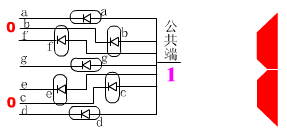

下图是LED数码管的内部结构及显示数码的情况,其是一个阳极连在一体的一种LED数码管,我们通常称为共阳极数码管。既然有共阳数码管,那么就有共阴数码管,这里没有画出其内部结构,请你自行画一下。

6、LED译码驱动器

发光二极管点亮只须使其正向导通即可,根据LED的公共极是阳极还是阴极分为两类译码器,即针对共阳极的低电平有效的译码器;针对共阴极LED的高电平输出有效的译码器。

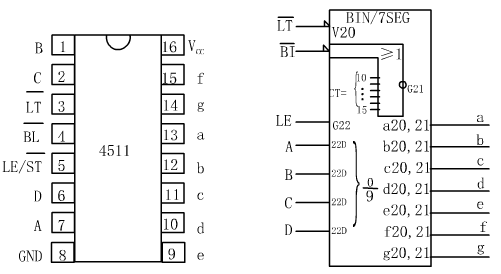

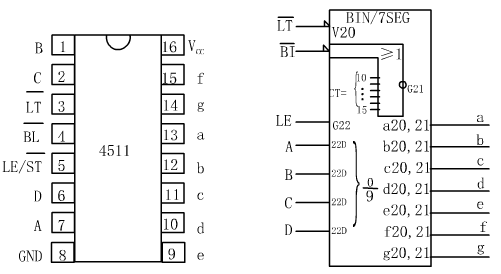

4511是输出高电平有效的CMOS显示译码器,其输入为8421BCD码,下图和表分别4511的管脚排布、逻辑符号和逻辑功能表。

| 输 入 |

译 码 输 出 |

| 使能输入 |

变量输入 |

| /LT |

/BL |

/ST/LE |

D |

C |

B |

A |

a |

b |

c |

d |

e |

f |

g |

| 1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

| 1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

| 1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

| 1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

| 1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

| 1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

| 1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

| 0 |

× |

× |

× |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

× |

× |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

| 1 |

1 |

1 |

× |

× |

× |

× |

※ |

※ |

※ |

※ |

※ |

※ |

※ |

| ※ 表示状态锁定在LE=0时,D~A的状态 |

图中:

/LT:试灯极,低电平有效,当其为低电平时,所有笔划全部亮,如不亮表示该笔划有问题;

/BL:灭灯极,低电平有效,当其为低电平时,不管输入的数据状态如何,其输出全为低电平,即所有笔划熄灭;

/ST/LE:选通/锁存极,其是一个复用的功能端,当输入为低电平时,其输出与输入的变量有关;当输入为高电平时,其输出仅与该端为高电平前的状态,并且输入DCBA端不管如何变化,其显示数值保持不变。

D,C,B,A:8421BCD码输入,其D位为最位;

a~g:输出端,为高电平有效,故其输出应与其阴极的数码管相对应。

7、LCD译码驱动器*

LCD译码驱动器电路与LED的译码驱动电路不同,其输出不是高电平或低电平,而是脉冲电压,当输出有效时,其输出为交变的脉冲电压,否则为高电平或低电平。 |

Alexa

Alexa mcusy_cn#126.com (请把#改成@)

mcusy_cn#126.com (请把#改成@)  交流:522422171

交流:522422171 51/AVR单片机技术驿站! <

51/AVR单片机技术驿站! <

最新评论

最新评论